Wistron 14088-1 TAHOE_MT H110主板工作流程简述

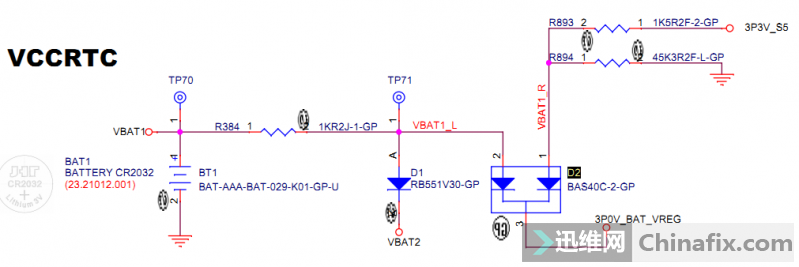

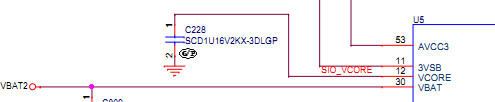

1、没插电源前,由3V纽扣电池BT1过电阻R384产生VBAT1_L,VBAT1_L过二极管D1产生VBAT2,送到IO芯片U5(IT8617E)的30(VBAT)脚;

VBAT2过二极管D2产生3P0V_BAT_VREG,给桥的BA22(VCCRTC)脚RTC电路供电。

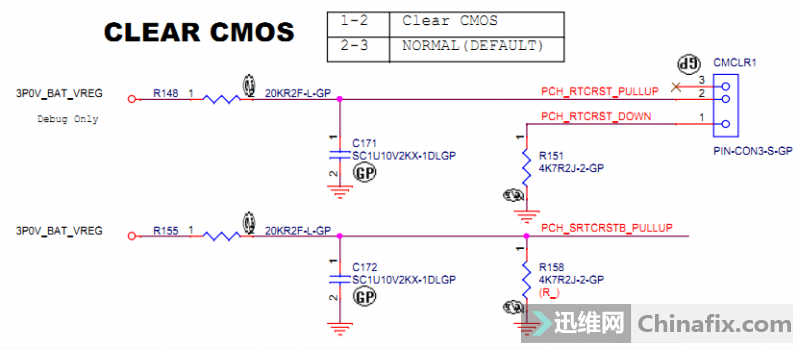

2、3P0V_BAT_VREG经过电阻R148,连接CMOS跳帽,给桥的BC10(RTCRST#)提供高电平RTCRST#。

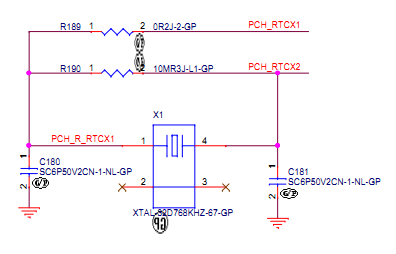

3、桥给晶振X1供电,晶振X1起振,产生32.768KHz给桥

4、插入ATX1,输出V_12P0_A待机供电。

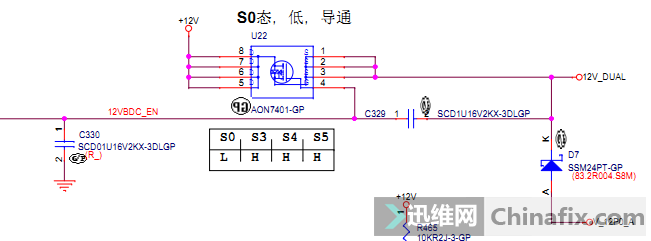

V_12P0_A经D7产生双通道供电的12V_DUAL。

12V_DUAL过PR130等改名PWR_5V3D3V_VIN。

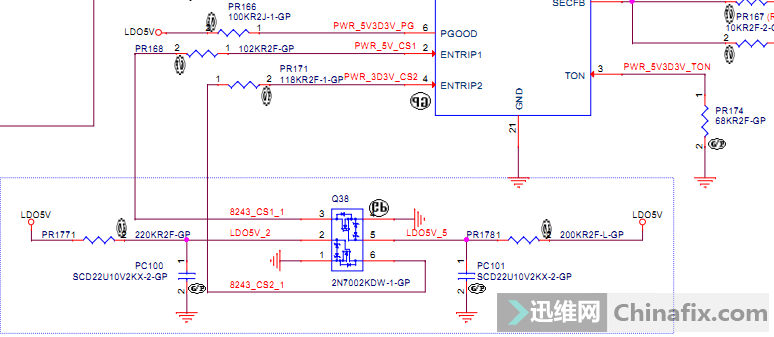

PWR_5V3D3V_VIN给待机芯片PU35(RT8243B)供电,PU35(RT8243B)从14(LDO5)输出LDO5V电压。

LDO5V控制Q38导通,产生PWR_5V_CS1、PWR_3D3V_CS2送到PU35(RT8243B)的2(ENTRIP1)、4(ENTRIP2)脚,开启PU35(RT8243B)工作,PU35(RT8243B)控制MOS输出PWR_5V和PWR_3D3V。

PWR_5V过PR5418等改名5V_S5;PWR_3D3V过PR138等改名3P3V_S5。

5V_S5、3P3V_S5为本机的待机电压。(触发后的电压由+12V通过U22(12V_DUAL)双通道供电产生)。

5、3P3V_S5作为深度睡眠待机电压给桥(VCCDSW_3P3)引脚W15和BA24脚;3P3V_S5还送到IO芯片U5(IT8617E)的11(3VSB)脚。

①IO芯片U5(IT8617E)检测到电压正常后,从第7(DPWROK/GP23)脚发出深度睡眠待机电压好PCH_SIO_DPWROK信号给到桥的AV11(DSW_PWROK)脚。

②桥从BB13(SLP_SUS#)脚发出SLP_SUSB,送到IO芯片U5(IT8617E)的64脚。

③SLP_SUSB送到U57(TPS22966DP)的6(ON2)脚,控制U57产生主待机电压3P3V_SB,送到桥的VCCPRIM_3P3引脚BD3、BE3、BE4和其它引脚。

④主待机电压3P3V_SB供给IO芯片U5(IT8617E)的28(SYS_3VSB)脚。

⑤3P3V_SB过0ohm电阻R482后改名3P3V_PCIVAUX供给PCI、PCI_E槽。

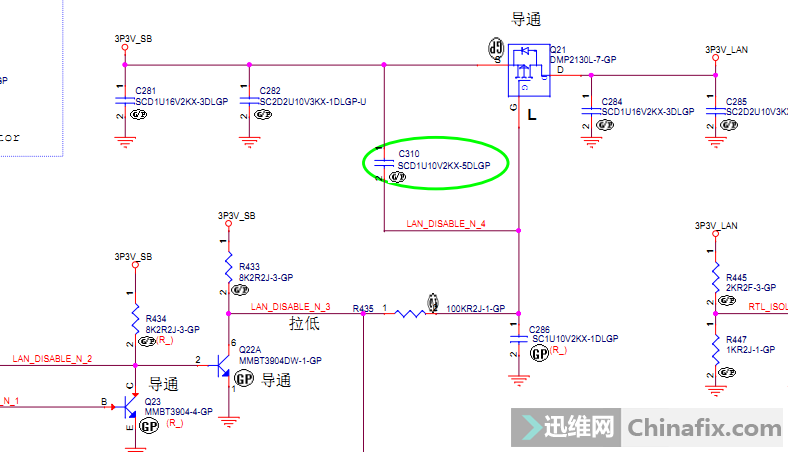

⑥3P3V_SB经过电路转换控制Q21导通,产生3P3V_LAN,供给网卡芯片U10(RTL8111G)的第32(AVDD33)脚。

⑦3P3V_SB过0ohm电阻R368后改名3P3V_SPI,供给桥的VCCSPI引脚BE41、BE42、BE43。

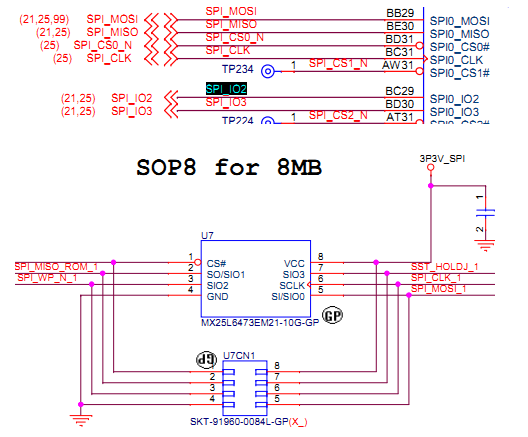

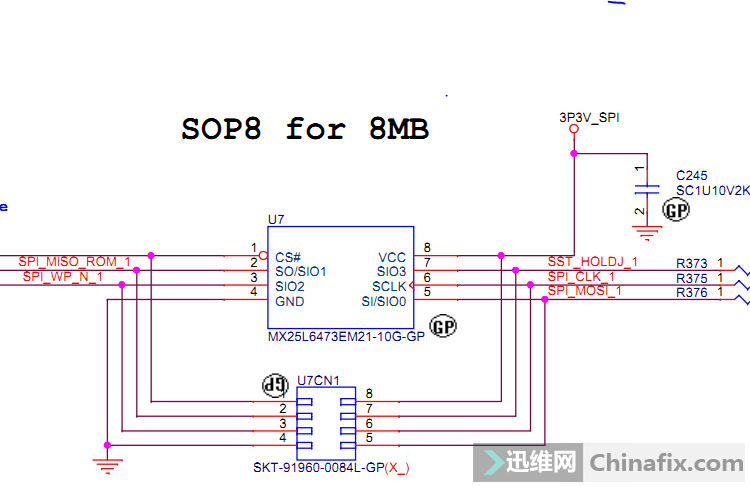

⑧3P3V_SPI给BIOS芯片U7供电。

★3V待机电压3P3V_SB正常后,再降压产生1V待机电压VCCPRIM_1P0:

PU14(RT8237C)控制产生PWR_1D0V电压,过PR213等后改名V1P0_PCH_SB,送给桥的VCCPRIM_1P0引脚供电。通过转换后给桥的其它引脚供电。

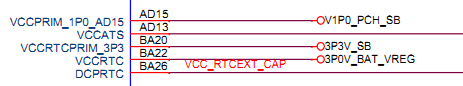

6、IO芯片U5检测待机电压正常后,从42(RSMRST#)脚发出待机电压好(RSMRST#)RSMRST_SIO_N信号,给桥的BA11(RSMRST#)脚。

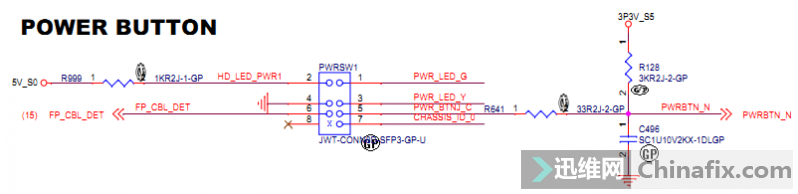

7、用户按下面板PWRSW1上的开关,产生3.3V_0V_3.3V跳变的信号PWRBTN_N,送到了IO芯片(IT8617E)的34(PANSWH#)脚。

8、IO从32(PWRON#)发出3.3V_0V_3.3V跳变的请求开机信号PWRBTN_N_SIO,送到了PCH的AT13(PWRBTN#)脚。

9、桥发出允许开机信号SLP_S*#:

①PCH从BB13(SLP_SUS#)脚发出SLP_SUSB信号;

②从AW15(SLP_S3#)脚发出SLP_S3_N信号;

③从BD15(SLP_4S#)脚发出SLP_S4_N信号;

其中SLP_SUSB送到IO的64(VLDT_EN/SLP_SUS#/GP63)脚。SLP_S3#送给IO的34(PANSWH#)脚。表示允许开机。

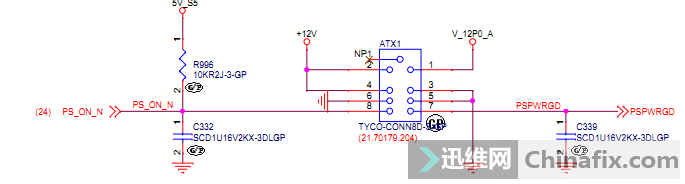

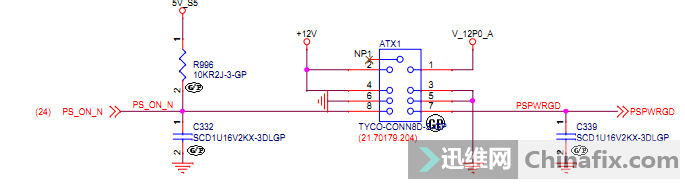

10、IO芯片从35(PSON#)脚发出持续低电平PS_ON_N信号,送到ATX1插头的8(PSON#)脚,拉低绿线开机。

11、ATX1从2、4脚输出:+12V。

12、①SLP_SUSB送到U57(TPS22966DP)控制产生5V_S0和3P3V_SB。

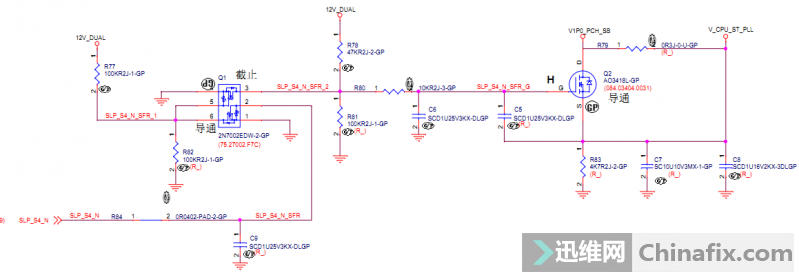

②SLP_S4#控制Q1、Q2将V1P0_PCH_SB转换V_CPU_ST_PLL,给PCH的1.05V的 VCCST/VCCPLL引脚供电。

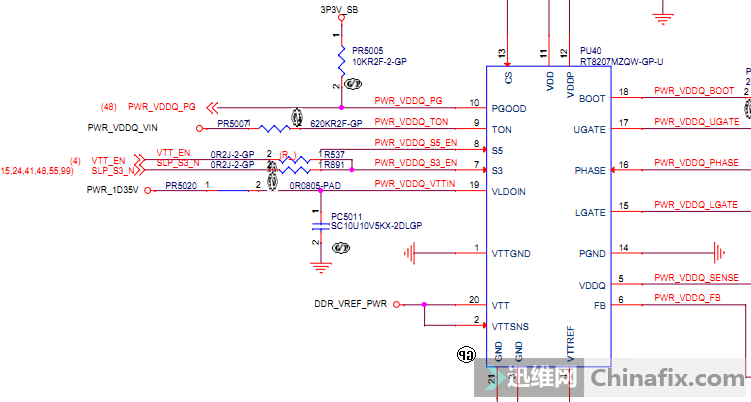

③SLP_S4过0ohm电阻R885改名PWR_VDDQ_S5_EN,送到PU40(RT8207M)的8(S5)脚;SLP_S3_N送到7(S3)脚,共同开启PU40工作,驱动PU39和PU41输出PWR_1D35V内存主供电。

PWR_1D35V内存主供电产生后,过PR191等节点改名V_SM,为CPU的VDDQ引脚和内存的VDD引脚供电。

V_SM_VTT的产生:CPU供电管理芯片的20(VTT)脚输出0D675V的DDR_VREF_PWR,过PR201节点改名V_SM_VTT. 为内存的VTT引脚供电。

④PU40(RT8207M)从第10(PGOOD)脚输出PWR_VDDQ_PG信号;从第20(VTT)脚输出DDR_VREF_PWR信号。

13、产生1.05V的VCCIO供电

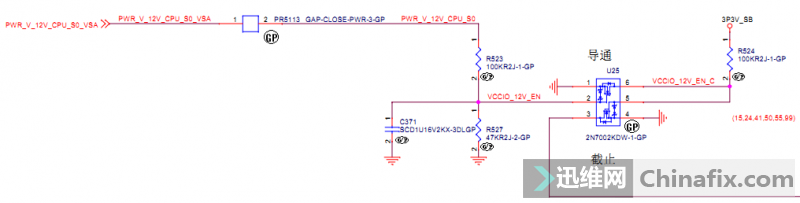

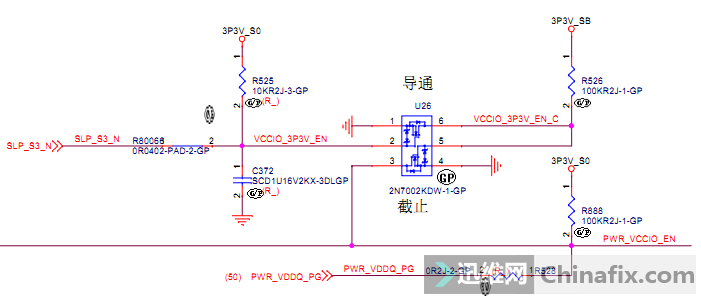

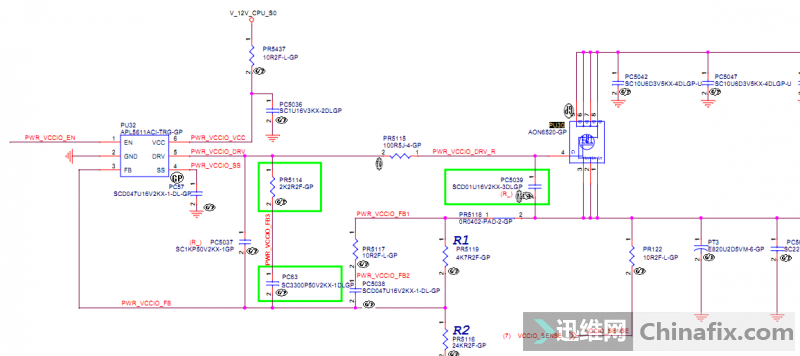

PWR_V_12V_CPU_S0_VSA控制U25,SLP_S3_N控制U26产生PWR_VCCIO_EN,去开启PU32(APL5611A)工作。

PU32控制PU30输出CPU的1.05V的VCCIO供电V_CPU_IO。供给CPU的VCCIO引脚。

14、1.05V桥核心供电正常后,控制产生VCCSA电压V_CPU_SA,并产生CPU供电的开启信号,但一般不会产生CPU供电,VBOOT=0V。

①SLP_S3_N控制U30产生VR_ENABLE信号;

②VR_ENABLE控制PQ1去开启PU28(RT8237),驱动PU27输出V_CPU_SA;

③V_CPU_SA给CPU的VCCSA引脚供电。

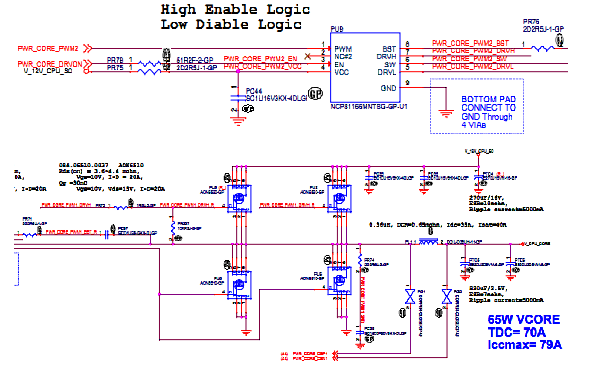

④VR_ENABLE送到CPU电源管理芯片PU1(NCP81203)的2(EN)脚,去开启PU1工作,但此时不会产生CPU供电,VBOOT=0V。

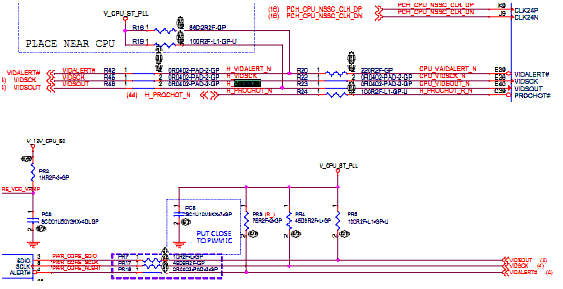

15、CPU电源管理芯片PU1(NCP81203)的6(VRDY)脚发出VR_READY信号,经U3转换发出高电平的PCH_PWROK信号,送到PCH的AW11(PCH_PWROK)脚,表示芯片已经准备好,产生CPU供电。

16、ATX1电源从第7脚延时发出灰线的PSPWRGD,送给IO芯片(IT8617E)的6(ATXPG/GP53)脚。

17、IO检测各路电压和PSPWRGD正常后,从37(PWRGD3/CPU_PG/SDA0)脚发出PWROK3信号,过0ohm电阻改名PCH_SYSPWROK,送给桥的AY1(SYS_PWROK)脚。

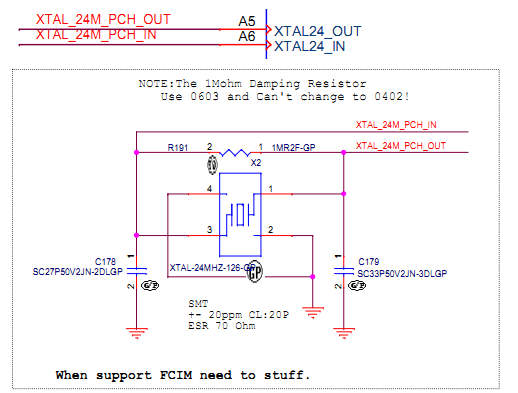

18、桥的24M昌振X2起振,桥读取BIOS芯片U7的数据。

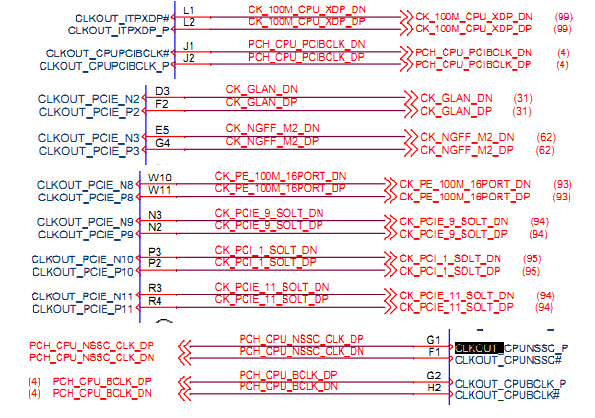

19、①桥发出时钟信号,送给主板各设备。

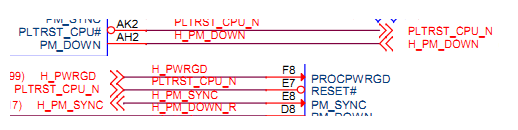

②桥从AM3(PROCPWRGD)脚发出H_PWRGD信号,送给CPU的F8(PROCPWRGD)脚。

③CPU发出SVID信号VIDSOUT、VIDSCK 、VIDALERT#给CPU供电芯片PU1的3(SDIO)、5(SCLK)、4(ALERT#)脚。

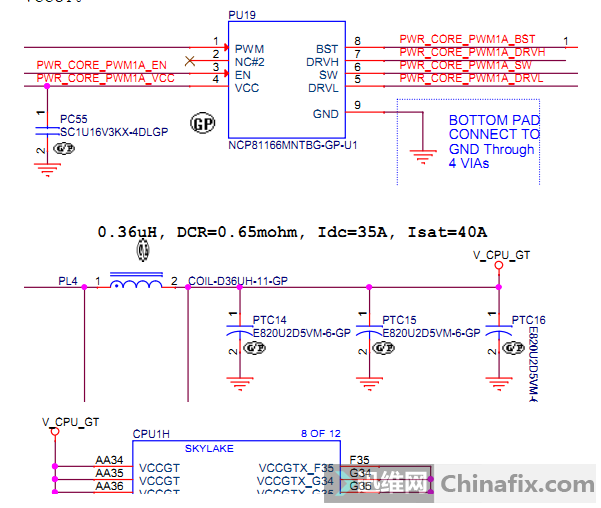

④CPU供电芯片PU1(NCP81203)控制输出CPU供电。

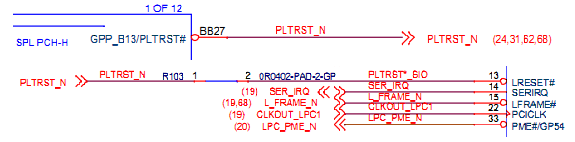

20、①桥发出平台复位(PLTRST#)PLTRST_N给IO芯片的13(LRESET#)脚,复位IO。

②PLTRST_N送到网卡芯片U10的19(PERST#)脚复位网卡。

PLTRST_N复位NGFF1芯片。还送到LPC1的3脚。

③IO芯片(IT8617E)从10脚输出PLTRST_PCIE_SLOTS_N信号,送到PCIE槽的A11脚,复位PCI_E槽。

PLTRST_PCIE_SLOTS_N信号还送到U54(XIO2001)的H11(PERST#)脚,复位U54(XIO2001)。

21、桥从AK22脚发出CPU的复位(PLTRST_CPU#)PLTRST_CPU_N信号,送到CPU的E7(RESET#)脚,复位CPU。

22、CPU开始工作,通过桥读取BIOS,开始自检跑码。

23、H110自检过内存后,CPU发出第二次SVID,控制产生集显供电VCCGT。

|